Example 1: The Circuit FOO¶

We start with a very simple logic circuit which we call "FOO"

- Inputs gates: $x_1$, $x_2$, $x_3$

- Output gates: $y_1$, $y_2$

- Logic action: $(y_1, y_2) = (x_1 \land x_2 , \ \neg x_3)$

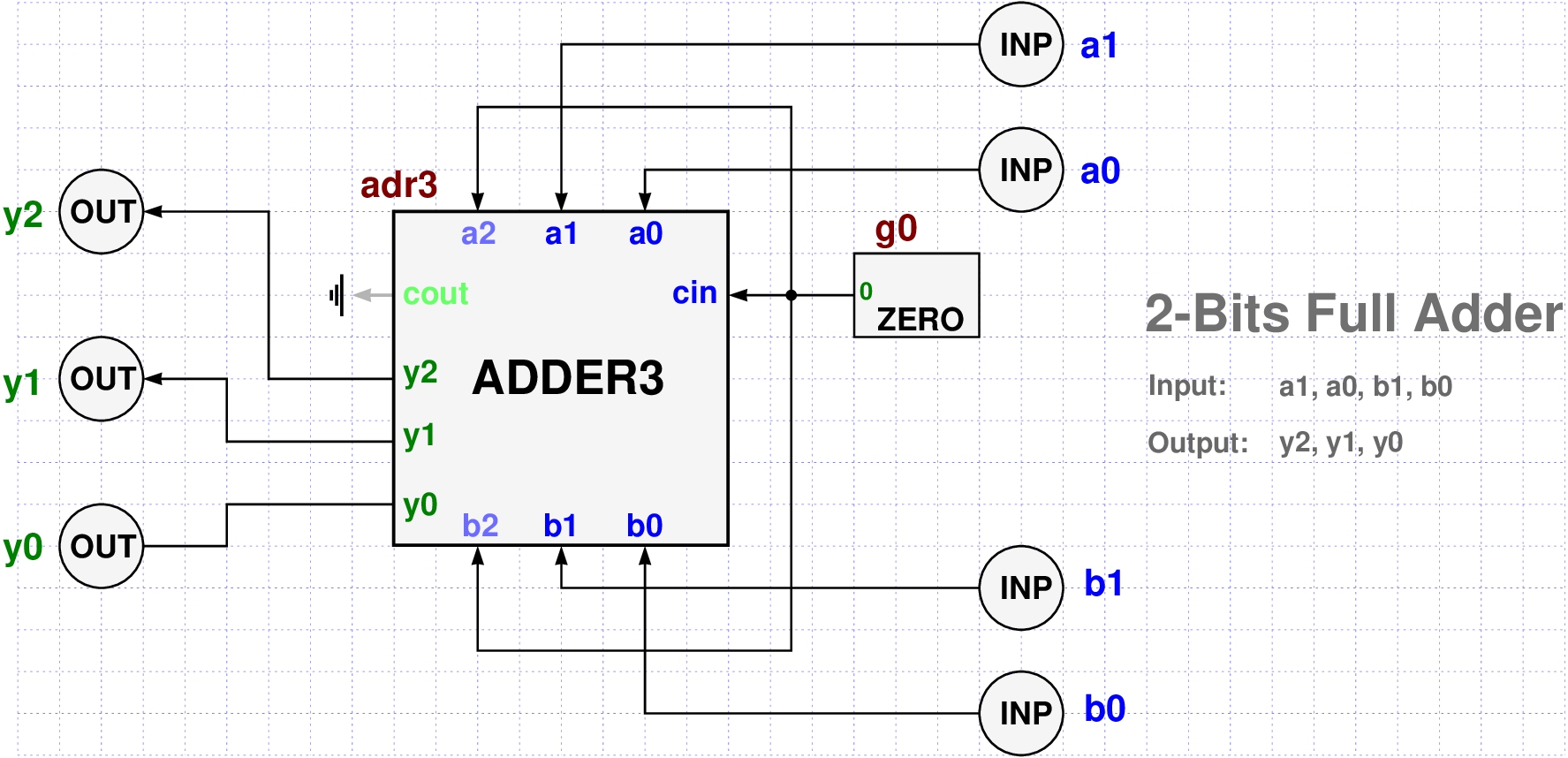

This circuit can be represented by the following PyCirc Diagram

A PyCirc diagram is a simplified form of circuit diagram in which gates are represented by text blocks rather than special shape symbols.

- Many students find the usual gate symbols intimidating and hard to memorize.

- Plain text on a circle or a rectangle seems to be more convenient, especially for computation theory courses in which most of the participants do not have any electronics background (or plan to go in this direction).

- Input and output gates are represented by circles with an INP/OUT labels.

- The other logic gates are represented by rectangular blocks with input/output pins near the block edges.

- Input gate names are blue colored.

- Output gate names are green colored.

- Logic gate names are brown colored.

- Connections ("Wires") are represented by arrowed lines from source pin to target pin.

- A pin is either an input/output gate or a named entry/exit point to a logic gate.

- In the above diagram we have 5 wires and 10 pins:

- 3 Input gates: x1, x2, x3

- 2 output gates: y1, y2

- 5 Block pins: g1/x1, g1/x2, g1/y, g2/x, g2/y

- Note the special notation g/p for the block pins.

- g stands for the gate name and p is the input/ouput name of the cell type of the gate.

- Here is the PyCirc code for modeling this circuit: